疑似AMD Zen 4處理器設計專利曝光升級5nm EUV加入L4快取記憶體

在今年 3 月份的 FAD 2020 大會 AMD 首次在官方路線圖放上 Zen 4 架構,由於 AMD 已確認 Zen 4 將升級 5nm 製程並會更換新的 CPU Socket,所以過去一段時間都有不少關於 Zen 4 處理器的消息傳出,例如有可能支援 DDR5 記憶體、PCIe 5.0 傳輸、AVX-512 等等,近日一位 Twitter 用家 Twitter@Underfox 在 AMD 一份新的專利申請上發現, AMD 將會在未來推出的新處理器虛擬環境中,新增 L4 Cache 高速緩存。

目前為止,AMD Zen 2 處理器每個 CCD 上含有 2 個 CCX,一個 CCX 有 4 個 CPU 核心。而一個 CCD 上面的兩個 CCX 之間共享 L3 Cache。之前的爆料則指 AMD 將會大改下一代的 Zen 3 架構,將原本的分離式的 L3 Cache 改成了整個 CCD 共享同一組 L3 Cache。

至於再下一代的 Zen 4 架構,由於升級用上 TSMC 的 5nm EUV 製程,在晶體管密度比 7nm 增加 80% 的情況下,AMD 將可以再核心數量最多一倍,有消息更指,Zen 4 將統一 L3 Cache 以服務整個 CCD ( 2 組 CCX )。

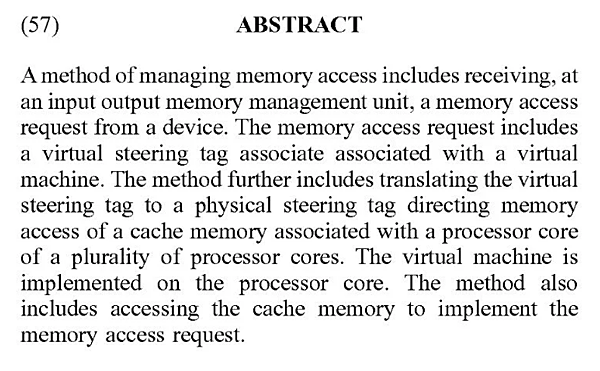

Twitter@Underfox 最新在 AMD 申請的新專利上發現,由於要支援 Virtualized environments 虛擬環境,AMD 將會在未來的新 CPU 上新增 L4 Cache 的可能性,該 L4 Cache 可協助處理在 CCD 上 L3 Cache 緩存未命中或發生錯誤的數據,提供最佳的高速緩存命中機會,而 L4 Cache 是為整個 CPU 提供服務。

外媒 ownsnap 在較早前就分析了為何 AMD 會在 Zen 4 架構加入 L4 Cache,主要的原因是用作解決基於 Zen 4 的新 Ryzen 及 EPYC 處理器不斷增加的核心數量,而目前的 CPU 平台仍然使用 L3 Cache,AMD 未來若果在 Zen 4 處理器再增加核心數量及提升時脈的時候,可能就需要 L4 Cache 相互補充了。

需要留意的是,AMD 新專利上提到的 L4 Cache 主要針對多個用戶共享同一處理器或一組處理器的虛擬化環境,因此目前尚不清楚如何為所有 CCD 配備通用的 L4 Cache 可以提升整體性能。

來源

謝謝收看

留言列表

留言列表