Nanosheet奈米片取代FinFET台積電挑戰物理極限2nm計劃2024年量產

目前台積電(TSMC)及三星(Samsung)在5nm、7nm製程,都依賴1999年發明的FinFET技術,到了3nm FinFET三面柵控制作用減弱,短通道效應再次突顯,因此在3nm及以下製程微縮變得更困難。繼IBM先前宣佈突破3nm極限,率先做出全球首款2nm晶片,日前網路上舉行TSMC 2021 Technology Symposium技術論壇,公佈未來新製程進展,台積電除了官宣6nm、5nm、4nm、3nm製程技術最新進展,同時對外公佈2nm製程有重大突破,對於今年在台灣建造2nm半導體試生產線。

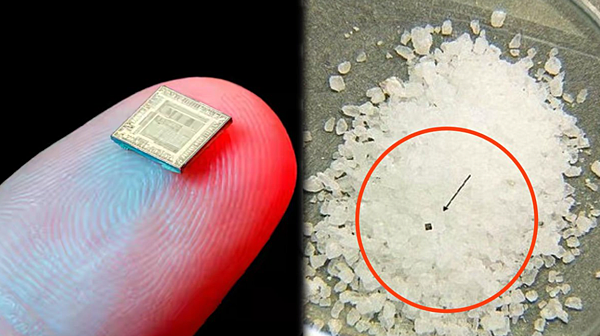

台積電說目前完成3nm製程,能支援智慧手機及HPC高性能運算集群應用,比較5nm製程,3nm邏輯密度提升1.7 倍,同時快了10% - 15%的速度,但功耗降低25% - 30%,台積電一直開發可靠符合規範低功耗晶片作為研發目標,穩步實現中。仔細評估客戶的需求、技術性能和成熟度之後,預計3nm製程2022年投入量產。

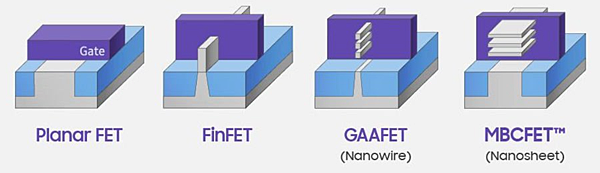

面對3nm製程面臨的挑戰,台積電說FinFET技術暫時只會用到3nm,2nm將會用全新技術,特點是會首次引入Nanosheet奈米片晶體管取代現有的FinFET。

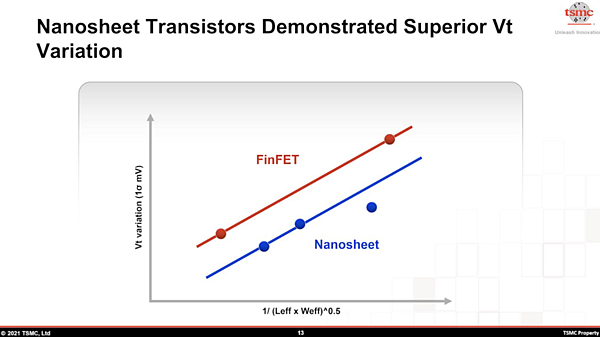

台積電也說,在Nanosheet奈米片取得重大突破,2nm是採用以GAA環繞閘極製程為基礎的MBCFET架構,可以解決FinFET因製程微縮產生電流控制漏電的物理極限問題。與FinFET晶體管(下圖紅線)相比,Nanosheet(下圖藍線)能實現更嚴格的閾值電壓(Vt)控制。

據了解,Vt 特指半導體電路工作所需的最小電壓,即使是最輕微的變化,也會對晶片的設計造成束縛、並導致性能的下降。不過,台積電有望通過設計及技術上的改良將 Nanosheet 奈米層片的效能提高超過 10% - 15%,並且更加穩定,台積電更稱之為史上最大的飛躍。

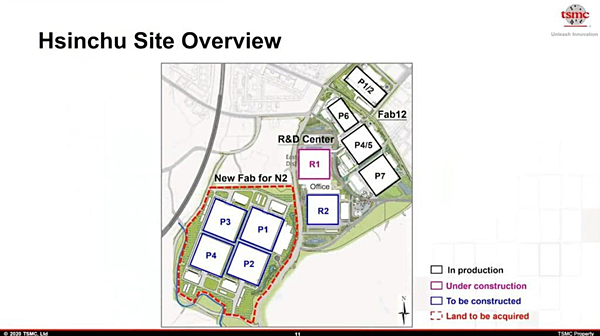

目前,台積電位於台灣台南的 Fab 18 晶圓廠將負責 3nm 製程的生產,目前還負責製造 5nm 的產品,並會進一步擴充產能。台積電亦計劃在台灣新竹興建立名為 Fab 20 的新晶圓廠,負責 2nm 製程的生產。

事實上,早在去年 9 月就有消息稱台積電在 2nm 半導體製造上取得重大研發突破,有望在 2023 年中期進入 2nm 工藝試生產階段,並在 2024 年開始批量生產。而隨著今年年內 2nm 超尖端半導體試生產線的建成,台積電的步伐可能會來得更快。

來源

謝謝收看

留言列表

留言列表